# **High Noise Immunity,** 3.3 V / 5 V Logic Gate **Optocoupler**

# **FOD8001**

#### Description

The FOD8001 is a 3.3 V / 5 V high-speed logic gate optocoupler, which supports isolated communications allowing digital signals to communicate between systems without conducting ground loops or hazardous voltages. It utilizes ON Semiconductor patented coplanar packaging technology, Optoplanar<sup>®</sup>, and optimized IC design to achieve high noise immunity, characterized by high common mode rejection and power supply rejection specifications.

This high-speed logic gate optocoupler, packaged in a compact 8-pin small outline package, consists of a high-speed AlGaAs LED driven by a CMOS buffer IC coupled to a CMOS detector IC. The detector IC comprises an integrated photodiode, a high-speed transimpedance amplifier and a voltage comparator with an output driver. The CMOS technology coupled to the high efficiency of the LED achieves low power consumption as well as very high speed (40ns propagation delay, 6ns pulse width distortion).

#### **Features**

- High Noise Immunity characterized by Common Mode Rejection (CMR) and Power Supply Rejection (PSR) Specifications

- ◆ 20 kV/µs Minimum Static CMR @ Vcm = 1000 V

- 25 kV/us Typical Dynamic CMR @ Vcm = 1500 V, 20 MBaud Rate

- PSR in Excess of 10% of the Supply Voltages across Full Operating Bandwidth

- High Speed:

- ◆ 25 Mbit/s Date Rate (NRZ)

- 40 ns max. Propagation Delay

- 6 ns max. Pulse Width Distortion

- 20 ns max. Propagation Delay Skew

- 3.3 V and 5 V CMOS Compatibility

- Extended Industrial Temperate Range, -40°C to 105°C Temperature Range

- Safety and Regulatory Pending Approvals:

- UL1577, 3750 VACRMS for 1 min.

- ◆ IEC60747-5-2 (pending)

#### **Applications**

- Industrial Fieldbus Communications

- Profibus, DeviceNet, CAN, RS485

- Programmable Logic Control

- Isolated Data Acquisition System

#### **TRUTH TABLE**

| VI   | LED | v <sub>o</sub> |

|------|-----|----------------|

| HIGH | OFF | HIGH           |

| LOW  | ON  | LOW            |

## ON Semiconductor®

#### www.onsemi.com

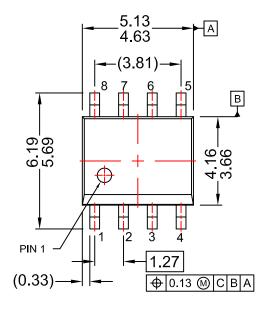

SOIC8 CASE 751DZ

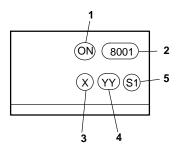

#### MARKING DIAGRAM

- = ON Semiconductor Logo 1. ON

- 8001 = Device Number 2.

- = One-Digit Year Code, e.g. '8' 3. Χ

- 4. YY = Two Digit Work Week Ranging

- from '01' to '53'

- = Assembly Package Code 5. S1

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 8 of this data sheet.

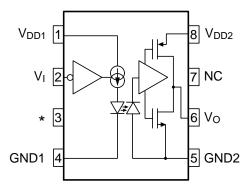

#### **Functional Schematic**

\*: Pin 3 must be left unconnected

Figure 1. Functional Schematic

## **PIN DEFINITIONS**

| Pin Number | Pin Name  | Pin Function Description             |

|------------|-----------|--------------------------------------|

| 1          | $V_{DD1}$ | Input Supply Voltage                 |

| 2          | VI        | Input Data                           |

| 3          |           | LED Anode – Must be left unconnected |

| 4          | GND1      | Input Ground                         |

| 5          | GND2      | Output Ground                        |

| 6          | Vo        | Output Data                          |

| 7          | NC        | Not Connected                        |

| 8          | $V_{DD2}$ | Output Supply Voltage                |

# ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise specified)

| Symbol             | Parameter                                                     | Value                          | Units |

|--------------------|---------------------------------------------------------------|--------------------------------|-------|

| T <sub>STG</sub>   | Storage Temperature                                           | -40 to +125                    | °C    |

| T <sub>OPR</sub>   | Operating Temperature                                         | -40 to +105                    | °C    |

| T <sub>SOL</sub>   | Lead Solder Temperature (Refer to Reflow Temperature Profile) | 260 for 10 s                   | °C    |

| $V_{DD1}, V_{DD2}$ | Supply Voltage                                                | 0 to 6.0                       | V     |

| V <sub>I</sub>     | Input Voltage                                                 | -0.5 to V <sub>DD1</sub> + 0.5 | V     |

| lį                 | Input DC Current                                              | -10 to +10                     | μΑ    |

| V <sub>O</sub>     | Output Voltage                                                | -0.5 to V <sub>DD2</sub> + 0.5 | V     |

| Io                 | Average Output Current                                        | 10                             | mA    |

| PDI                | Input Power Dissipation (Note 1)                              | 90                             | mW    |

| PDO                | Total Power Dissipation (Note 2)                              | 70                             | mW    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Derate linearly from 25°C at a rate of tbd W/°C

- 2. Derate linearly from 25°C at a rate of tbd mW/°C

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol                              | Parameter                                  | Min. | Max.            | Unit |

|-------------------------------------|--------------------------------------------|------|-----------------|------|

| T <sub>A</sub>                      | Ambient Operating Temperature              | -40  | +105            | °C   |

| V <sub>DD1</sub> , V <sub>DD2</sub> | Supply Voltages (3.3 V Operation) (Note 3) | 3.0  | 3.6             | V    |

|                                     | Supply Voltages (5.0 V Operation) (Note 3) | 4.5  | 5.5             |      |

| V <sub>IH</sub>                     | Logic High Input Voltage                   | 2.0  | V <sub>DD</sub> | V    |

| V <sub>IL</sub>                     | Logic Low Input Voltage                    | 0    | 0.8             | V    |

| t <sub>r</sub> , t <sub>f</sub>     | Input Signal Rise and Fall Time            |      | 1.0             | ms   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3.  $0.1\,\mu\text{F}$  bypass capacitor must be connected between Pin 1 and 4, and 5 and 8.

# ISOLATION CHARACTERISTICS (Apply over all recommended conditions, typical value is measured at T<sub>A</sub> = 25°C)

| Symbol           | Characteristics                | Test Conditions                                                                            | Min.             | Тур. | Max. | Unit               |

|------------------|--------------------------------|--------------------------------------------------------------------------------------------|------------------|------|------|--------------------|

| V <sub>ISO</sub> | Input-Output Isolation Voltage | $f = 60 \text{ Hz}, t = 1.0 \text{ min.}, I_{I-O} \le 10 \mu\text{A} \text{ (Notes 4, 5)}$ | 3750             |      |      | Vac <sub>RMS</sub> |

| R <sub>ISO</sub> | Isolation Resistance           | V <sub>I-O</sub> = 500V (Note 4)                                                           | 10 <sup>11</sup> |      |      | Ω                  |

| C <sub>ISO</sub> | Isolation Capacitance          | V <sub>I-O</sub> = 0 V, f = 1.0MHz (Note 4)                                                |                  | 0.2  |      | pF                 |

- 4. Device is considered a two terminal device: Pins 1, 2, 3 and 4 are shorted together and Pins 5, 6, 7 and 8 are shorted together.

- 5.  $3,750 \text{ VAC}_{RMS}$  for 1 minute duration is equivalent to  $4,500 \text{ VAC}_{RMS}$  for 1 second duration.

**ELECTRICAL CHARACTERISTICS** (Apply over all recommended conditions, typical value is measured at  $V_{DD1} = V_{DD2} = +3.3 \text{ V}$ ,  $V_{DD1} = +3.3 \text{ V}$  and  $V_{DD2} = +5.0 \text{ V}$ ,  $V_{DD1} = +5.0 \text{ V}$ ,  $V_{D1} = +5.0 \text{ V}$ ,  $V_{$

| 22.                 | 222                              | 222 22                                                              | •    |      |      |       |

|---------------------|----------------------------------|---------------------------------------------------------------------|------|------|------|-------|

| Symbol              | Parameter                        | Conditions                                                          | Min. | Тур. | Max. | Units |

| INPUT CH            | ARACTERISTICS                    |                                                                     |      |      |      |       |

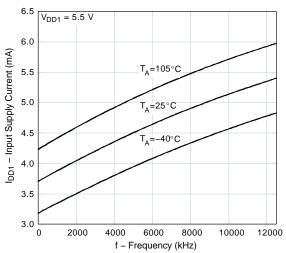

| I <sub>DD1L</sub>   | Logic Low Input Supply Current   | V <sub>I</sub> = 0 V                                                |      | 6.2  | 10.0 | mA    |

| I <sub>DD1H</sub>   | Logic High Input Supply Current  | $V_I = V_{DD1}$                                                     |      | 0.8  | 3.0  | mA    |

| $I_{IA}$ , $I_{IB}$ | Input Current                    |                                                                     | -10  |      | +10  | μΑ    |

| OUTPUT C            | HARACTERISTICS                   | •                                                                   | •    |      | •    | •     |

| I <sub>DD2L</sub>   | Logic Low Output Supply Current  | V <sub>I</sub> = 0 V                                                |      | 4.5  | 9.0  | mA    |

| I <sub>DD2H</sub>   | Logic High Output Supply Current | $V_I = V_{DD1}$                                                     |      | 4.5  | 9.0  | mA    |

| V <sub>OH</sub>     | Logic High Output Voltage        | $I_{O} = -20 \mu A$ , $V_{I} = V_{IH}$ , $V_{DD2} = +3.3 \text{ V}$ | 2.9  | 3.3  |      | V     |

|                     |                                  | $I_{O} = -4 \text{ mA}, V_{I} = V_{IH}, V_{DD2} = +3.3 \text{ V}$   | 1.9  | 2.9  |      |       |

|                     |                                  | $I_{O} = -20 \mu A$ , $V_{I} = V_{IH}$ , $V_{DD2} = +5.0 \text{ V}$ | 4.4  | 5.0  |      |       |

|                     |                                  | $I_{O} = -4 \text{ mA}, V_{I} = V_{IH}, V_{DD2} = +5.0 \text{ V}$   | 4.0  | 4.8  |      |       |

| V <sub>OL</sub>     | Logic Low Output Voltage         | $I_O = 20 \mu A$ , $V_I = V_{IL}$                                   |      | 0    | 0.1  | V     |

|                     |                                  | $I_0 = 4 \text{ mA}$ , $V_1 = V_1$                                  |      | 0.3  | 1.0  |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

**SWITCHING CHARACTERISTICS** (Apply over all recommended conditions, typical value is measured at  $V_{DD1} = V_{DD2} = +3.3 \text{ V}$ ,  $V_{DD1} = +3.3 \text{ V}$  and  $V_{DD2} = +5.0 \text{ V}$ ,  $V_{DD1} = +5.0 \text{ V}$ ,  $V_{D1} = +5.0 \text{ V}$ ,

| Symbol           | Parameter                                                     | Test Conditions                                                                    | Min. | Тур. | Max. | Unit  |

|------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|-------|

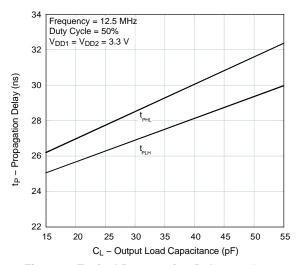

| t <sub>PHL</sub> | Propagation Delay Time to Logic Low Output                    | C <sub>L</sub> = 15 pF                                                             |      | 25   | 40   | ns    |

| t <sub>PLH</sub> | Propagation Delay Time to Logic High Output                   | C <sub>L</sub> = 15 pF                                                             |      | 25   | 40   | ns    |

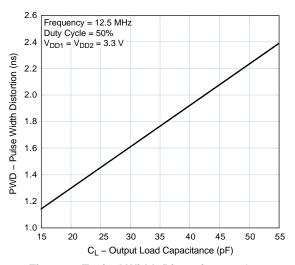

| PWD              | Pulse Width Distortion,   t <sub>PHL</sub> - t <sub>PLH</sub> | PWD = 40 ns, C <sub>L</sub> = 15 pF                                                |      | 2    | 6    | ns    |

|                  | Data Rate                                                     |                                                                                    |      |      | 25   | Mb/s  |

| t <sub>PSK</sub> | Propagation Delay Skew                                        | C <sub>L</sub> = 15 pF <sup>(6)</sup>                                              |      |      | 20   | ns    |

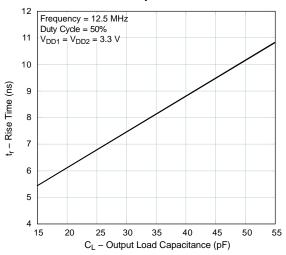

| t <sub>R</sub>   | Output Rise Time (10%–90%)                                    |                                                                                    |      | 6.5  |      | ns    |

| t <sub>F</sub>   | Output Fall Time (90%–10%)                                    |                                                                                    |      | 6.5  |      | ns    |

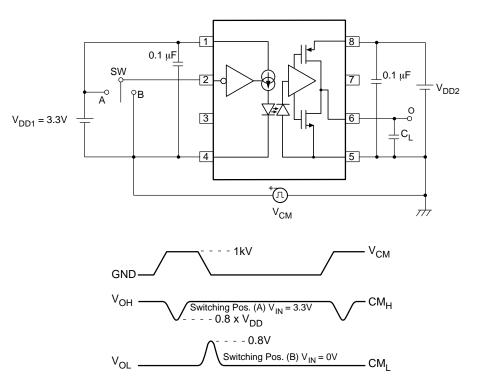

| CM <sub>H</sub>  | Common Mode Transient Immunity at Output High                 | $V_I = V_{DD1}, V_O > 0.8 V_{DD1}, V_{CM} = 1000 V (Note 7)$                       | 20   | 40   |      | kV/μs |

| CM <sub>L</sub>  | Common Mode Transient Immunity at Output Low                  | V <sub>I</sub> = 0 V, V <sub>O</sub> < 0.8 V,<br>V <sub>CM</sub> = 1000 V (Note 7) | 20   | 40   |      | kV/μs |

| C <sub>PDI</sub> | Input Dynamic Power Dissipation<br>Capacitance (Note 8)       |                                                                                    |      | 30   |      | pF    |

| C <sub>PDO</sub> | Output Dynamic Power Dissipation<br>Capacitance (Note 8)      |                                                                                    |      | 3    |      | pF    |

<sup>6.</sup> t<sub>PSK</sub> is equal to the magnitude of the worst case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that will be seen between units at any given temperature within the recommended operating conditions.

<sup>7.</sup> Common mode transient immunity at output high is the maximum tolerable positive dVcm/dt on the leading edge of the common mode impulse signal, Vcm, to assure that the output will remain high. Common mode transient immunity at output low is the maximum tolerable negative dVcm/dt on the trailing edge of the common pulse signal, Vcm, to assure that the output will remain low.

<sup>8.</sup> Unloaded dynamic power dissipation is calculated as follows: C<sub>PD</sub> x V<sub>DD</sub> x f + I<sub>DD</sub> + V<sub>PD</sub> where f is switched time in MHz.

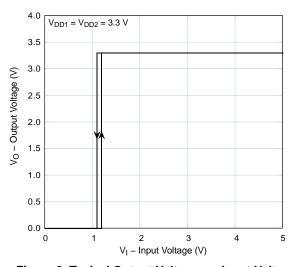

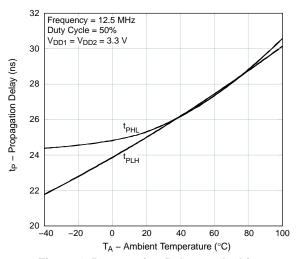

## **TYPICAL PERFORMANCE CURVES**

Figure 2. Typical Output Voltage vs. Input Voltage

Figure 4. Propagation Delay vs. Ambient Temperature

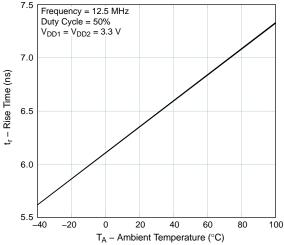

Figure 6. Typical Rise Time vs. Ambient Temperature

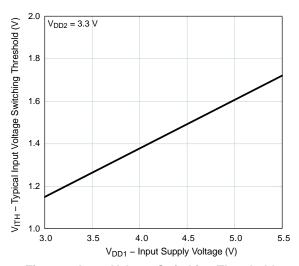

Figure 3. Input Voltage Switching Threshold vs. Input Supply Voltage

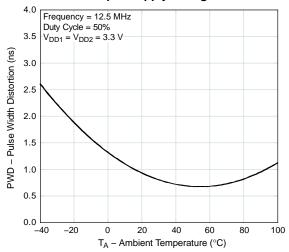

Figure 5. Pulse Width Distortion vs. Ambient Temperature

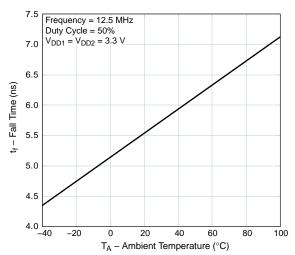

Figure 7. Typical Fall Time vs. Ambient Temperature

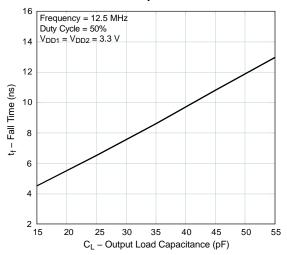

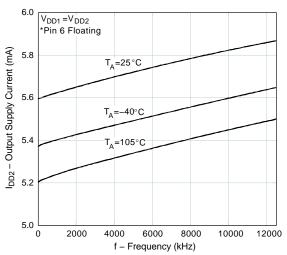

# TYPICAL PERFORMANCE CURVES (Continued)

Figure 8. Typical Propagation Delay vs. Output Load Capacitance

Figure 10. Typical Rise Time vs. Output Load Capacitance

Figure 12. Input Supply Current vs. Frequency

Figure 9. Typical Width Distortion vs. Output Load Capacitance

Figure 11. Typical Fall Time vs. Output Load Capacitance

Figure 13. Output Supply Current vs. Frequency

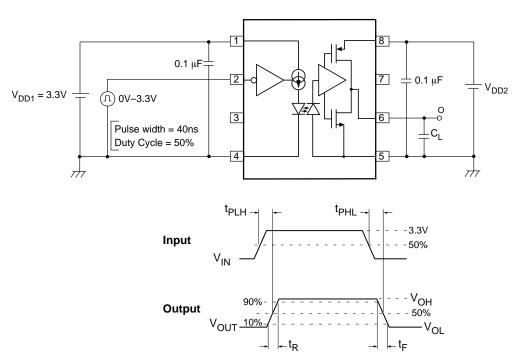

# **TEST CIRCUITS**

Figure 14. Test Circuit for Propagation Delay and Rise Time, Fall Time

Figure 15. Test Circuit for Instantaneous Common Mode Rejection Voltage

#### APPLICATION INFORMATION

Noise is defined as any unwanted signal that degrades or interferes with the operation of a system or circuit. Input—output noise rejection is a key characteristic of an optocoupler, and the performance specification for this noise rejection is called, "Common Mode Transient Immunity or Common Mode Rejection, CMR". The CMR test configuration is presented in high speed optocoupler datasheets, which tests the optocoupler to a specified rate of interfering signal (dv/dt), at a specified peak voltage (Vcm).

This defined noise signal is applied to the test device while the coupler is a stable logic high or logic low state. This test procedure evaluates the interface device in a constant or static logic state. This type of CMR can be referred to as "Static CMR". ON Semiconductor high speed optocouplers, which use an optically transparent, electrically conductive shield, and offer active totem pole logic output have static CMR in excess of  $50 \text{ kV/}\mu\text{s}$  at peak amplitudes of 1.5 kV to 2.0 kV.

# **Dynamic Common Mode Rejection**

The noise susceptibility of an interface while it is actively transferring data is a common requirement in serial data communication. However, the static CMR specification is not adequate in quantifying the electrical noise susceptibility for optocouplers used in isolating high speed data transfer.

A serial data communication network's noise performance is usually quantified as the number of bit errors per second or as a ratio of the number of bits transmitted in a specified time frame. This describes Bit Error Rate, BER. Test equipment that evaluates BER is called a Bit Error Rate Tester, BERT. When a BERT system is combined with a CMR tester, the active or dynamic noise rejection of an isolated interface can then be quantified. This type of CMR is thus defined as "Dynamic CMR". Therefore, evaluating the common mode rejection while the optocoupler is switching at high speed represents a realistic approach to understand noise interference.

Test circuit functions were built to interface a commercial pseudo-random bit sequence (PRBS) generator and error detector with a pair of high speed optocouplers, FOD8001, connected in a loop-back configuration. With a 10 MBaud PRBS serial data stream, no error was detected until the common mode voltage rose above 2.5 kV with a dv/dt of 45 kV/ $\mu$ s. And increasing the data rate beyond 10 Mbaud, the test was conducted at 20 MBaud, and no error was detected at dv/dt of 25 kV/ $\mu$ s at common mode voltage of 1.5 kV.

The test data for the dynamic CMR is comparable or better than the static CMR specifications found in the datasheet. These excellent noise rejection performances are results of the innovative circuit design and the patented coplanar assembly process.

## **Power Supply Noise Rejection**

High levels of electrical noise can cause the optocoupler to register the incorrect logic state. The most commonly discussed noise signal is the common mode noise found between the input and output of the optocoupler. However, common mode noise is not the only path of noise into the input or output of the optocoupler. Due to the high gain and wide bandwidth of the transimpedance amplifier used for the photo detector circuits, power supply noise can cause the optocoupler to change state independent of the LED operation. Power supply noise is typically characterized as either random or periodic pulses with varying amplitudes and rates of rise and fall. The necessary tests have been conducted to understand the influence of the power supply noise and its effect of the proper operation of the FOD8001. The optocoupler under test offered power supply noise rejection in excess of 10% of the supply voltage for a frequency ranging from 100 kHz to 35 MHz, for logic high and logic low states.

# **ORDERING INFORMATION**

| Option    | Order Entry Identifier | Package          | Packing Method <sup>†</sup>          |

|-----------|------------------------|------------------|--------------------------------------|

| No Suffix | FOD8001                | SOIC8 (Pb-Free)* | Tube (50 Units per Tube)             |

| R2        | FOD8001R2              | SOIC8 (Pb-Free)* | Tape and Reel (2,500 Units per Reel) |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## **REFLOW PROFILE**

OPTOPLANAR is a registered trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

<sup>\*</sup>All packages are lead free per JEDEC: J-STD-020B standard.

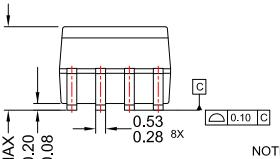

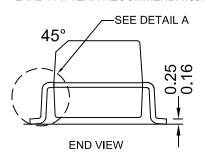

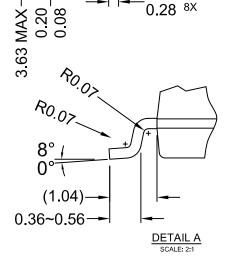

SOIC8 CASE 751DZ ISSUE O

**DATE 30 SEP 2016**

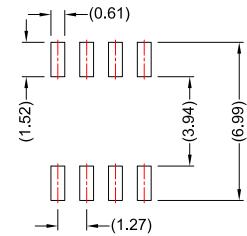

LAND PATTERN RECOMMENDATION

- A) NO STANDARD APPLIES TO THIS PACKAGE

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS.

- D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

| DOCUMENT NUMBER: | 98AON13733G | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC8       |                                                                                                                                                                                   | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative